## inta 8XC198 COMMERCIAL/EXPRESS CHMOS MICROCONTROLLER

## 8 Kbytes of OTPROM

- 8 Kbytes of On-Chip OTPROM or ROM

- 232 Byte Register File

- Register-to-Register Architecture

- 28 Interrupt Sources/16 Vectors

- 1.75 µs 16 x 16 Multiply (16 MHz)

- 3.0 µs 32/16 Divide (16 MHz)

- Powerdown and Idle Modes

- 16-Bit Watchdog Timer

- 8-Bit External Bus

- 16 MHz Standard

- Full Duplex Serial Port

- High Speed I/O Subsystem

- 16-Bit Timer

- 16-Bit Counter

- Pulse-Width-Modulated Output

- Four 16-Bit Software Timers

- 10-Bit A/D Converter with Sample/Hold

- Extended Temperature Available

The 8XC198 family offers low-cost entry into Intel's powerful MCS®-96 16-bit microcontroller architecture. Intel's CHMOS process provides a high performance processor along with low power consumption. To further reduce power requirements, the processor can be placed into Idle or Powerdown Mode.

The 8XC198 is the 8-bit bus version of the 8XC196KB. The prefixes mean: 80 (ROMIess), 83 (ROM), 87 (OTP) One Time Programmable. The ROM and OTP are available in 8 Kbytes.

Bit, byte, word and some 32-bit operations are available on the 8XC198. With a 16 MHz oscillator a 16-bit addition takes 0.50  $\mu$ s, and the instruction times average 0.37  $\mu$ s to 1.1  $\mu$ s in typical applications.

Four high-speed capture inputs are provided to record times when events occur. Six high-speed outputs are available for pulse or waveform generation. The high-speed output can also generate four software timers or start an A/D conversion. Events can be based on the timer or counter. Also provided on-chip are an A/D converter, serial port, watchdog timer and a pulse-width-modulated output signal.

With the commercial (standard) temperature option, operational characteristics are guaranteed over the temperature range of 0°C to +70°C. Wth the extended temperature range option, operational characteristics are guaranteed over the temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

MCS®-96 is a registered trademark of Intel Corporation.

\*Other brands and names are the property of their respective owners. Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products. Intel retains the right to make changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata. COPYRIGHT © INTEL CORPORATION, 1995 October 1992 Order Number: 272034-003

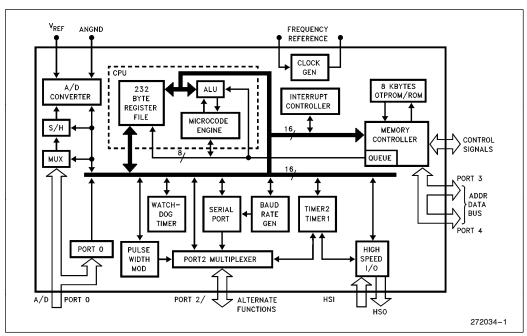

Figure 1. 87C198 Block Diagram

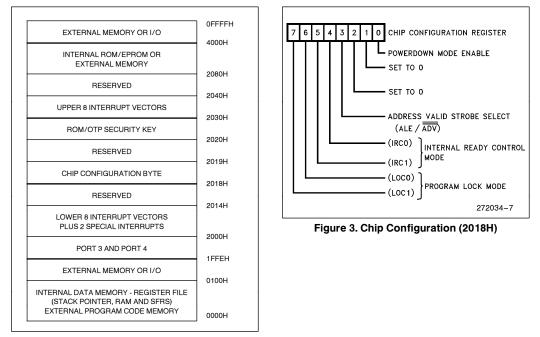

Figure 2. Memory Map

#### WARNING:

Reserved memory locations must not be written or read. The contents and/or function of these locations may change with future revisions of the device. Therefore, a program that relies on one or more of these locations may not function properly.

## int

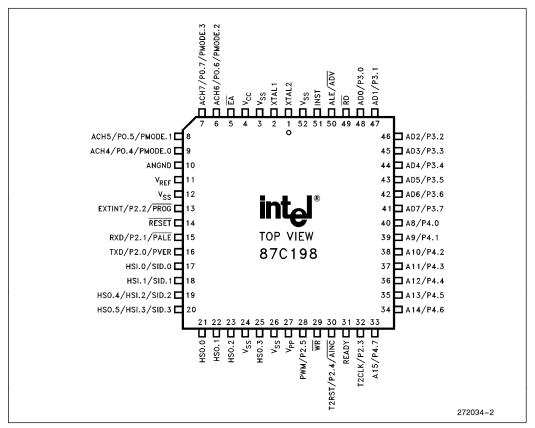

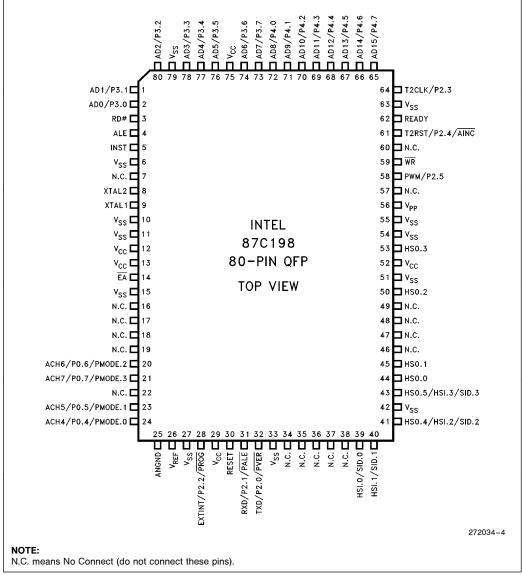

## PACKAGING

The 8XC198 is available in a 52-pin PLCC package and an 80-pin QFP package. Contact your local sales office to determine the exact ordering code for the part desired.

Package Designators:

N = 52-pin PLCCS = 80-pin QFP

#### **Thermal Characteristics**

| Package Type | $\theta_{ja}$ | $\theta_{jc}$ |

|--------------|---------------|---------------|

| PLCC         | 40°C/W        |               |

| QFP          | 70°C/W        | 4°C/W         |

All thermal impedance data is approximate for static air conditions at 1W of power dissipation. Values will change depending on operating conditions and application. See the Intel Packaging Handbook (Order Number 240800) for a description of Intel's thermal impedance test methodology.

Figure 4. 52-Pin PLCC Package

#### NOTE:

The above pinout diagram applies to the OTP (87C198) device. The OTP device uses all of the programming pins shown above. The ROM (83C198) device only uses programming pins: **AINC, PALE, PMODE.n** and **PROG**. The ROMless (80C198) doesn't use any of the programming pins.

Figure 5. 80-Pin QFP Package

#### NOTE:

The above pinout diagram applies to the OTP (87C198) device. The OTP device uses all of the programming pins shown above. The ROM (83C198) device only uses programming pins: **AINC, PALE, PMODE.n** and **PROG**. The ROMless (80C198) doesn't use any of the programming pins.

## **PIN DESCRIPTIONS**

| Symbol           | Name and Function                                                                                                                                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub>  | Main supply voltage (5V).                                                                                                                                                                                                                                                                   |

| V <sub>SS</sub>  | The PLCC package has 5 $\rm V_{SS}$ pins and the QFP package has 12 $\rm V_{SS}$ pins. All must be connected to digital ground.                                                                                                                                                             |

| V <sub>REF</sub> | Reference voltage for the A/D converter (5V). $V_{REF}$ is also the supply voltage to the analog portion of the A/D converter and the logic used to read Port 0. Must be connected for A/D and Port 0 to function.                                                                          |

| ANGND            | Reference ground for the A/D converter. Must be held at nominally the same potential as $V_{\mbox{SS}}.$                                                                                                                                                                                    |

| V <sub>PP</sub>  | Programming Voltage. Also, timing pin for the return from powerdown circuit.                                                                                                                                                                                                                |

| XTAL1            | Input of the oscillator inverter and of the internal clock generator.                                                                                                                                                                                                                       |

| XTAL2            | Output of the oscillator inverter.                                                                                                                                                                                                                                                          |

| RESET            | Reset input to and open-drain output from the chip. Input low for at least 4 state times to reset the chip. The subsequent low-to-high transition commences the 10-state Reset Sequence.                                                                                                    |

| INST             | Output high during an external memory read indicates the read is an instruction fetch.<br>INST is valid throughout the bus cycle. INST is activated only during external memory accesses and output low for a data fetch.                                                                   |

| ĒĀ               | Input for memory select (External Access). EA equal to a TTL-high causes memory accesses to locations 2000H through 3FFFH to be directed to on-chip ROM/EPROM. EA equal to a TTL-low causes accesses to these locations to be directed to off-chip memory.                                  |

| ALE/ADV          | Address Latch Enable or Address Valid output, as selected by CCR. Both pin options provide a latch to demultiplex the address from the address/data bus. When the pin is ADV, it goes inactive high at the end of the bus cycle. ALE/ADV is activated only during external memory accesses. |

| RD               | Read signal output to external memory. $\overline{\text{RD}}$ is activated only during external memory reads.                                                                                                                                                                               |

| WR               | Write output to external memory. $\overline{\text{WR}}$ will go low for every external write.                                                                                                                                                                                               |

| READY            | Ready input to lengthen external memory cycles. When the external memory is not being used, READY has no effect. Internal control of the number of wait states inserted into a bus cycle held not ready is available through configuration of CCR.                                          |

| HSI              | Inputs to High Speed Input Unit. Four HSI pins are available: HSI.0, HSI.1, HSI.2 and HSI.3. Two of them (HSI.2 and HSI.3) are shared with the HSO Unit.                                                                                                                                    |

| HSO              | Outputs from High Speed Output Unit. Six HSO pins are available: HSO.0, HSO.1, HSO.2, HSO.3, HSO.4 and HSO.5. Two of them (HSO.4 and HSO.5) are shared with the HSI Unit.                                                                                                                   |

| Port 0           | 4-bit high impedance input-only port. These pins can be used as digital inputs and/or as analog inputs to the on-chip A/D converter. These pins set the Programming Mode on the EPROM device.                                                                                               |

| Symbol                              | Name and Function                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port 2                              | Multi-functional port. All of its pins are shared with other functions in the 80C198.                                                                                                                                                                                                                                                    |

| Ports 3 and 4                       | 8-bit bidirectional I/O ports with open drain outputs. These pins are shared with the multiplexed address/data bus which has strong internal pullups. Available as I/O only on the ROM and EPROM devices.                                                                                                                                |

| TxD                                 | The TxD pin is used for serial port transmission in Modes 1, 2 and 3. In mode 0 the pin is used as the serial clock output.                                                                                                                                                                                                              |

| RxD                                 | Serial Port Receive pin used for serial port reception. In mode 0 the pin functions as input or output data.                                                                                                                                                                                                                             |

| EXTINT                              | A positive transition on the EXTINT pin will generate an external interrupt.                                                                                                                                                                                                                                                             |

| T2CLK                               | The T2CLK pin is the Timer2 clock input or the serial port baud rate generator input.                                                                                                                                                                                                                                                    |

| T2RST                               | A rising edge on the T2RST pin will reset Timer2.                                                                                                                                                                                                                                                                                        |

| PWM                                 | The PWM output.                                                                                                                                                                                                                                                                                                                          |

| PMODE                               | Programming Mode Select. Determines the EPROM programming algorithm that is performed. PMODE is sampled after a chip reset and should be static while the part is operating.                                                                                                                                                             |

| SID                                 | Slave ID Number. Used to assign each slave a pin of Port 3 or 4 to use for passing programming verification acknowledgement.                                                                                                                                                                                                             |

| PALE                                | Programming ALE Input. Accepted by the 87C196KB when it is in Slave<br>Programming Mode. Used to indicate that Ports 3 and 4 contain a command/<br>address.                                                                                                                                                                              |

| PROG                                | Programming. Falling edge indicates valid data on PBUS and the beginning of programming. Rising edge indicates end of programming.                                                                                                                                                                                                       |

| PVAL                                | Program Valid. This signal indicates the success or failure of programming in the Auto Programming Mode. A zero indicates successful programming.                                                                                                                                                                                        |

| PVER                                | Program Verification. Used in Slave Programming and Auto CLB Programming<br>Modes. Signal is low after rising edge of PROG if the programming was not<br>successful.                                                                                                                                                                     |

| AINC                                | Auto Increment. Active low signal indicates that the auto increment mode is enabled. Auto Increment will allow reading or writing of sequential EPROM locations without address transactions across the PBUS for each read or write.                                                                                                     |

| PORTS 3 and 4<br>(when programming) | Address/Command/Data Bus. Used to pass commands, addresses, and data to and from slave mode 87C196KBs. Used by chips in Auto Programming Mode to pass command, addresses and data to slaves. Also used in the Auto Programming Mode as a regular system bus to access external memory. Should have pullups to $V_{CC}$ (15 k $\Omega$ ). |

## PIN DESCRIPTIONS (Continued)

#### 8XC198

## **ELECTRICAL CHARACTERISTICS**

### **ABSOLUTE MAXIMUM RATINGS\***

Ambient Temperature

| under Bias                                                                                     |

|------------------------------------------------------------------------------------------------|

| Storage Temperature $\dots -65^{\circ}C$ to $+150^{\circ}C$                                    |

| Voltage on V <sub>PP</sub> or $\overline{\text{EA}}$ to V <sub>SS</sub> or ANGND0.3V to +13.0V |

| Voltage on Any Other Pin to $V_{SS}\ \ldots -0.5V$ to $+7.0V$                                  |

| Power Dissipation <sup>(1)</sup> 1.5W                                                          |

|                                                                                                |

#### NOTE:

1. Power dissipation is based on package heat transfer limitations, not device power consumption. NOTICE: This data sheet contains preliminary information on new products in production. It is valid for the devices indicated in the revision history. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

#### **OPERATING CONDITIONS**

(All characteristics in this data sheet apply to these operating conditions unless otherwise noted.)

| Symbol           | Description                    | Min  | Max  | Units |

|------------------|--------------------------------|------|------|-------|

| T <sub>A</sub>   | Ambient Temperature Under Bias | 0    | + 70 | °C    |

| V <sub>CC</sub>  | Digital Supply Voltage         | 4.50 | 5.50 | V     |

| V <sub>REF</sub> | Analog Supply Voltage          | 4.50 | 5.50 | V     |

| Fosc             | Oscillator Frequency 16 MHz    | 3.5  | 16   | MHz   |

#### NOTE:

ANGND and  $V_{\mbox{SS}}$  should be nominally at the same potential.

## **DC CHARACTERISTICS**

| Symbol           | Description                                         | Min                                          | Max                | Units       | Test Conditions                                                         |

|------------------|-----------------------------------------------------|----------------------------------------------|--------------------|-------------|-------------------------------------------------------------------------|

| V <sub>IL</sub>  | Input Low Voltage                                   | -0.5                                         | 0.8                | V           |                                                                         |

| V <sub>IH</sub>  | Input High Voltage <sup>(1)</sup>                   | $0.2 V_{CC} + 0.9$                           | $V_{CC} + 0.5$     | V           |                                                                         |

| V <sub>IH1</sub> | Input High Voltage on XTAL1                         | 0.7 V <sub>CC</sub>                          | $V_{CC} + 0.5$     | V           |                                                                         |

| V <sub>IH2</sub> | Input High Voltage on RESET                         | 2.6                                          | $V_{CC} + 0.5$     | V           |                                                                         |

| V <sub>OL</sub>  | Output Low Voltage                                  |                                              | 0.3<br>0.45<br>1.5 | V<br>V<br>V | $I_{OL} = 200 \ \mu A$ $I_{OL} = 32 \ m A$ $I_{OL} = 7 \ m A$           |

| V <sub>OH</sub>  | Output High Voltage<br>(Standard Outputs)           | $V_{CC} - 0.3 \ V_{CC} - 0.7 \ V_{CC} - 1.5$ |                    | V<br>V<br>V | $I_{OH} = -200 \ \mu A$<br>$I_{OH} = -3.2 \ m A$<br>$I_{OH} = -7 \ m A$ |

| ILI              | Input Leakage Current (Std. Inputs)                 |                                              | ±10                | μΑ          | $0 < V_{\text{IN}} < V_{\text{CC}} - 0.3V$                              |

| I <sub>LI1</sub> | Input Leakage Current (Port 0)                      |                                              | +3                 | μΑ          | $0 < V_{IN} < V_{REF}$                                                  |

| l <sub>IL1</sub> | Logical 0 Input Current in Reset<br>(ALE, RD, INST) |                                              | -6                 | mA          | $V_{IN} = 0.45 V$                                                       |

| Hyst             | Hysteresis on RESET Pin                             | 300                                          |                    | mV          |                                                                         |

#### NOTE:

1. All pins except RESET and XTAL1.

### DC CHARACTERISTICS (Continued)

| Symbol            | Description                            | Min | Тур(6) | Max | Units | Test Conditions                    |

|-------------------|----------------------------------------|-----|--------|-----|-------|------------------------------------|

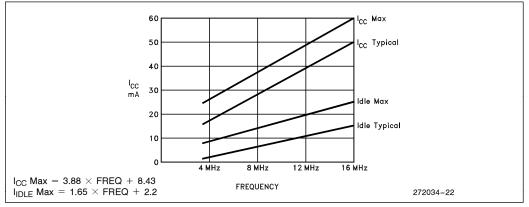

| ICC               | Active Mode Current in Reset           |     | 50     | 60  | mA    | XTAL1 = 16 MHz                     |

| I <sub>REF</sub>  | A/D Converter Reference Current        |     | 2      | 5   | mA    | $V_{CC} = V_{PP} = V_{REF} = 5.5V$ |

| I <sub>IDLE</sub> | Idle Mode Current                      |     | 10     | 25  | mA    |                                    |

| I <sub>CC1</sub>  | Active Mode Current                    |     | 15     | 25  | mA    | XTAL1 = 3.5 MHz                    |

| I <sub>PD</sub>   | Powerdown Mode Current                 |     | 5      | 30  | μΑ    | $V_{CC} = V_{PP} = V_{REF} = 5.5V$ |

| R <sub>RST</sub>  | Reset Pullup Resistor                  | 6K  |        | 50K | Ω     |                                    |

| CS                | Pin Capacitance (Any Pin to $V_{SS}$ ) |     |        | 10  | pF    | $F_{TEST} = 1.0 \text{ MHz}$       |

#### NOTES:

(Notes apply to all specifications)

1. Standard Outputs include AD0-15, RD, WR, ALE, INST, HSO pins, PWM/P2.5, RESET, Ports 3 and 4, TXD/P2.0 and RXD (in serial mode 0). The V<sub>OH</sub> specification is not valid for RESET. Ports 3 and 4 are open-drain outputs.

2. Standard Inputs include HSI pins, EA, READY, RXD/P2.1, EXTINT/P2.2, T2CLK/P2.3 and T2RST/P2.4.

3. Maximum current per pin must be externally limited to the following values if  $V_{OL}$  is held above 0.45V or  $V_{OH}$  is held

|   | HSO, P2.0, RXD, RESET   | I <sub>OL</sub> : 29 mA         | I <sub>OH</sub> : 26 mA |

|---|-------------------------|---------------------------------|-------------------------|

|   | P2.5, WR                | I <sub>OL</sub> : 13 mA         | I <sub>OH</sub> : 11 mA |

|   | AD0-AD15                | I <sub>OL</sub> : 52 mA         | I <sub>OH</sub> : 52 mA |

|   | RD, ALE, INST           | I <sub>OL</sub> : 13 mA         | I <sub>OH</sub> : 13 mA |

| ~ | Trustants and based and | Burn the of the same is a start |                         |

and  $V_{\text{REF}} = V_{\text{CC}} = 5V$ .

Figure 8. I<sub>CC</sub> and I<sub>IDLE</sub> vs Frequency

#### 8XC198

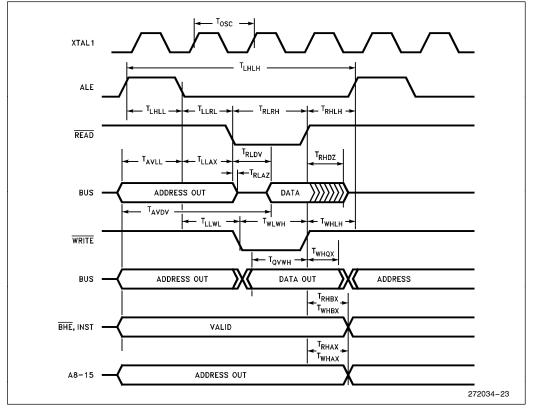

## **AC CHARACTERISTICS**

Test Conditions: Capacitive load on all pins = 100 pF, Rise and fall times = 10 ns,  $F_{OSC}$  = 12/16 MHz

| Symbol            | Description                                | Min                   | Мах                     | Units | Notes    |

|-------------------|--------------------------------------------|-----------------------|-------------------------|-------|----------|

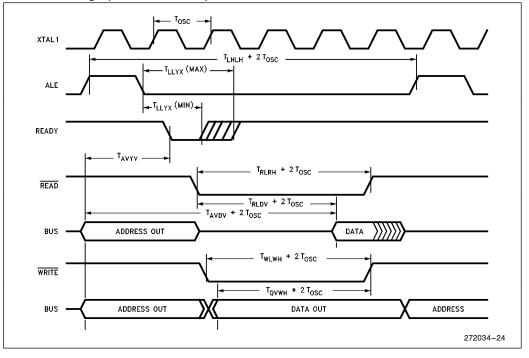

| T <sub>AVYV</sub> | Address Valid to Ready Setup               |                       | 2 T <sub>OSC</sub> — 75 | ns    |          |

| T <sub>YLYH</sub> | Non READY Time                             | No upper limit        |                         | ns    |          |

| T <sub>LLYX</sub> | READY Hold after ALE Low                   | T <sub>OSC</sub> - 15 | 2 T <sub>OSC</sub> - 40 | ns    | (Note 1) |

| T <sub>AVDV</sub> | Address Valid to Input Data Valid          |                       | 3 T <sub>OSC</sub> — 55 | ns    | (Note 2) |

| T <sub>RLDV</sub> | RD Active to Input Data Valid              |                       | $T_{OSC} - 23$          | ns    | (Note 2) |

| T <sub>RHDZ</sub> | End of $\overline{RD}$ to Input Data Float |                       | $T_{OSC} - 20$          | ns    |          |

| T <sub>RXDX</sub> | Data Hold after RD Inactive                | 0                     |                         | ns    |          |

### The system must meet these specifications to work with the 87C198:

NOTES:

1. If max is exceeded, additional wait states will occur. 2. When using wait states, add 2 T<sub>OSC</sub>  $\times$  n, where n = number of wait states.

### **AC CHARACTERISTICS**

Test Conditions: Capacitive load on all pins = 100 pF, Rise and fall times = 10 ns,  $F_{OSC} = 12/16$  MHz

| Symbol            | Description                                        | Min                   | Max                   | Units | Notes    |

|-------------------|----------------------------------------------------|-----------------------|-----------------------|-------|----------|

| F <sub>XTAL</sub> | Frequency on XTAL1 12 MHz                          | 3.5                   | 12                    | MHz   | (Note 1) |

| F <sub>XTAL</sub> | Frequency on XTAL1 16 MHz                          | 3.5                   | 16                    | MHz   | (Note 1) |

| T <sub>OSC</sub>  | 1/F <sub>XTAL</sub> <b>12 MHz</b>                  | 83.3                  | 286                   | ns    |          |

| T <sub>OSC</sub>  | 1/F <sub>XTAL</sub> 16 MHz                         | 62.5                  | 286                   | ns    |          |

| T <sub>LHLH</sub> | ALE Cycle Time                                     | 4 T                   | osc                   | ns    | (Note 3) |

| T <sub>LHLL</sub> | ALE High Period                                    | T <sub>OSC</sub> - 10 | T <sub>OSC</sub> +10  | ns    |          |

| T <sub>AVLL</sub> | Address Setup to ALE Falling Edge                  | T <sub>OSC</sub> - 20 |                       | ns    |          |

| T <sub>LLAX</sub> | Address Hold after ALE Falling Edge                | T <sub>OSC</sub> - 40 |                       | ns    |          |

| T <sub>LLRL</sub> | ALE Falling Edge to $\overline{RD}$ Falling Edge   | T <sub>OSC</sub> - 35 |                       | ns    |          |

| T <sub>RLRH</sub> | RD Low Period                                      | T <sub>OSC</sub> – 5  | T <sub>OSC</sub> + 25 | ns    | (Note 3) |

| T <sub>RHLH</sub> | RD Rising Edge to ALE Rising Edge                  | Tosc                  | T <sub>OSC</sub> + 25 | ns    | (Note 2) |

| T <sub>RLAZ</sub> | RD Low to Address Float                            |                       | 5                     | ns    |          |

| T <sub>LLWL</sub> | ALE Falling Edge to $\overline{WR}$ Falling Edge   | T <sub>OSC</sub> - 10 |                       | ns    |          |

| T <sub>QVWH</sub> | Data Stable to WR Rising Edge                      | T <sub>OSC</sub> - 23 |                       | ns    | (Note 3) |

| T <sub>WLWH</sub> | WR Low Period                                      | T <sub>OSC</sub> - 15 | T <sub>OSC</sub> + 5  | ns    | (Note 3) |

| T <sub>WHQX</sub> | Data Hold after WR Rising Edge                     | T <sub>OSC</sub> - 15 |                       | ns    |          |

| T <sub>WHLH</sub> | WR Rising Edge to ALE Rising Edge                  | T <sub>OSC</sub> - 15 | T <sub>OSC</sub> + 10 | ns    | (Note 2) |

| T <sub>WHBX</sub> | INST Hold after WR Rising Edge                     | T <sub>OSC</sub> - 15 |                       | ns    |          |

| T <sub>LLBX</sub> | INST Hold after ALE Rising Edge                    | T <sub>OSC</sub> - 10 |                       | ns    |          |

| T <sub>RHBX</sub> | INST Hold after $\overline{\text{RD}}$ Rising Edge | T <sub>OSC</sub> - 10 |                       | ns    |          |

| T <sub>WHAX</sub> | AD8–15 Hold after WR Rising Edge                   | T <sub>OSC</sub> - 30 |                       | ns    |          |

| T <sub>RHAX</sub> | AD8–15 Hold after RD Rising Edge                   | T <sub>OSC</sub> - 25 |                       | ns    |          |

The 87C198 will meet these specifications:

NOTES:

1. Testing performed at 3.5 MHz. However, the part is static by design and will typically operate below 1 Hz. 2. Assuming back-to-back bus cycles. 3. When using wait states, add 2  $T_{OSC} \times n$ , where n = number of wait states.

## System Bus Timings

## **READY Timings (One Wait State)**

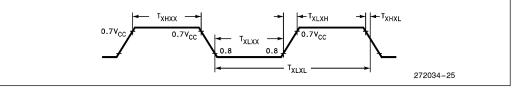

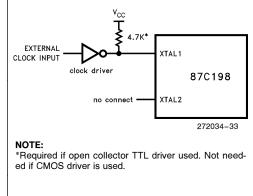

## **EXTERNAL CLOCK DRIVE**

| Symbol              | Parameter                   | Min   | Max  | Units |

|---------------------|-----------------------------|-------|------|-------|

| 1/T <sub>XLXL</sub> | Oscillator Frequency 12 MHz | 3.5   | 12.0 | MHz   |

| 1/T <sub>XLXL</sub> | Oscillator Frequency 16 MHz | 3.5   | 16.0 | MHz   |

| T <sub>XLXL</sub>   | Oscillator Period 12 MHz    | 83.3  | 286  | ns    |

| T <sub>XLXL</sub>   | Oscillator Period 16 MHz    | 62.5  | 286  | ns    |

| T <sub>XHXX</sub>   | High Time                   | 21.25 |      | ns    |

| T <sub>XLXX</sub>   | Low Time                    | 21.25 |      | ns    |

| T <sub>XLXH</sub>   | Rise Time                   |       | 10   | ns    |

| T <sub>XHXL</sub>   | Fall Time                   |       | 10   | ns    |

### EXTERNAL CLOCK DRIVE WAVEFORMS

An external oscillator may encounter as much as a 100 pF load at XTAL1 when it starts-up. This is due to interaction between the amplifier and its feedback capacitance. Once the external signal meets the V<sub>IL</sub> and V<sub>IH</sub> specifications the capacitance will not exceed 20 pF.

PRELIMINARY

12

#### 8XC198

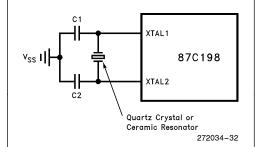

#### **EXTERNAL CRYSTAL CONNECTIONS**

#### NOTE:

Keep oscillator components close to chip and use short direct traces to XTAL1, XTAL2 and  $V_{SS}.$  When using crystals, C1 = 20 pF, C2 = 20 pF. When using ceramic resonators consult manufacturer for recommended capacitor values.

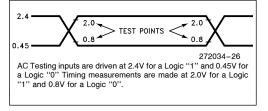

#### AC TESTING INPUT, OUTPUT WAVEFORMS

**EXTERNAL CLOCK CONNECTIONS**

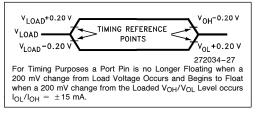

#### FLOAT WAVEFORMS

#### **EXPLANATION OF AC SYMBOLS**

Each symbol is two pairs of letters prefixed by "T" for time. The characters in a pair indicate a signal and its condition, respectively. Symbols represent the time between the two signal/condition points.

### Conditions:

- H High

- L Low

- V Valid

- X No Longer Valid

- Z Floating

## Signals:

| А | <ul> <li>Address</li> </ul> |

|---|-----------------------------|

| D | - DATA IN                   |

| L | - ALE/ADV                   |

| Q | - DATA OUT                  |

| R | - RD                        |

| W | - WR                        |

| х | - XTAL1                     |

Y - READY

#### 8XC198

#### **10-BIT AID CHARACTERISTICS**

At a clock speed of 6 MHz or less, the clock prescaler should be disabled. This is accomplished by setting IOC2.4 = 1.

At higher frequencies (greater than 6 MHz) the clock prescaler should be turned on (IOC2.4 = 0) to allow the comparator to settle.

The table below shows two different clock speeds and their corresponding A/D conversion and sample times.

state time =  $\frac{2}{f_{XTAL1}}$

State times are calculated as follows:

The converter is ratiometric, so the absolute accuracy is directly dependent on the accuracy and stability of V<sub>REF</sub>. V<sub>REF</sub> must be close to V<sub>CC</sub> since it supplies both the resistor ladder and the digital section of the converter.

See the MCS-96 A/D Converter Quick Reference for definition of A/D terms.

| AID Clock<br>Prescaler       | Clock Speed<br>(MHz) | Sample Time<br>(States) | Sample Time<br>at Clock<br>Speed (µs) | Conversion<br>Time<br>(States) | Conversion<br>Time at Clock<br>Speed (µs) |  |

|------------------------------|----------------------|-------------------------|---------------------------------------|--------------------------------|-------------------------------------------|--|

| $IOC2.4 = 0 \rightarrow ON$  | 16                   | 15                      | 1.875                                 | 156.5                          | 19.6                                      |  |

| $IOC2.4 = 1 \rightarrow OFF$ | 6                    | 8                       | 2.667                                 | 89.5                           | 29.8                                      |  |

## Example Sample and Conversion Times

### **A/D CONVERTER SPECIFICATIONS**

| Parameter                                                                       | Typical(1)              | Minimum    | Maximum    | Units*                     | Notes |

|---------------------------------------------------------------------------------|-------------------------|------------|------------|----------------------------|-------|

| Resolution                                                                      |                         | 1024<br>10 | 1024<br>10 | Levels<br>Bits             |       |

| Absolute Error                                                                  |                         | 0          | ±3         | LSBs                       |       |

| Full Scale Error                                                                | 0.25 ±0.50              |            |            | LSBs                       |       |

| Zero Offset Error                                                               | $-0.25 \pm 0.50$        |            |            | LSBs                       |       |

| Non-Linearity Error                                                             | 1.5 ±2.5                | 0          | ±3         | LSBs                       |       |

| Differential Non-Linearity Error                                                |                         | >-1        | +2         | LSBs                       |       |

| Channel-to-Channel Matching                                                     | ±0.1                    | 0          | ±1         | LSBs                       |       |

| Repeatability                                                                   | ±0.25                   |            |            | LSBs                       |       |

| Temperature Coefficients:<br>Offset<br>Full Scale<br>Differential Non-Linearity | 0.009<br>0.009<br>0.009 |            |            | LSB/°C<br>LSB/°C<br>LSB/°C |       |

| Off Isolation                                                                   |                         | -60        |            | dB                         | 2, 3  |

| Feedthrough                                                                     | -60                     |            |            | dB                         | 2     |

| V <sub>CC</sub> Power Supply Rejection                                          | -60                     |            |            | dB                         | 2     |

| Input Series Resistance                                                         |                         | 750        | 1.2K       | Ω                          | 4     |

| DC Input Leakage                                                                |                         | 0          | 3.0        | μΑ                         |       |

| Sample Time: Prescaler On<br>Prescaler Off                                      | 15<br>8                 |            |            | States<br>States           |       |

| Sampling Capacitor                                                              | 3                       |            |            | pF                         |       |

NOTES:

\*An "LSB", as used here, has a value of approximately 5 mV.

1. Typical values are expected for most devices at 25°C but are not tested or guaranteed.

2. DC to 100 KHz.

3. Multiplexer Break-Before-Make Guaranteed.

4. Resistance from device pin, through internal MUX, to sample capacitor.

## **EPROM SPECIFICATIONS**

## **EPROM PROGRAMMING OPERATING CONDITIONS**

| Symbol                                                   | Parameter                              | Min   | Мах  | Units |

|----------------------------------------------------------|----------------------------------------|-------|------|-------|

| Τ <sub>Α</sub>                                           | Ambient Temperature during Programming | 20    | 30   | °C    |

| V <sub>CC</sub> , V <sub>PD</sub> , V <sub>REF</sub> (1) | Supply Voltages during Programming     | 4.5   | 5.5  | V     |

| V <sub>EA</sub>                                          | Programming Mode Supply Voltage        | 12.50 | 13.0 | V(2)  |

| V <sub>PP</sub>                                          | EPROM Programming Supply Voltage       | 12.50 | 13.0 | V(2)  |

| V <sub>SS</sub> ,<br>ANGND <sup>(3)</sup>                | Digital and Analog Ground              | 0     | 0    | V     |

| F <sub>OSC</sub>                                         | Oscillator Frequency 16 MHz            | 6.0   | 16.0 | MHz   |

#### NOTES:

V<sub>CC</sub>, V<sub>PD</sub> and V<sub>REF</sub> should nominally be at the same voltage during programming.

V<sub>CA</sub> and V<sub>PP</sub> must never exceed the maximum voltage for any amount of time or the device may be damaged.

V<sub>SS</sub> and ANGND should nominally be at the same voltage (0V) during programming.

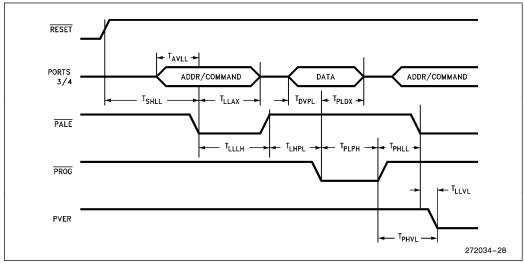

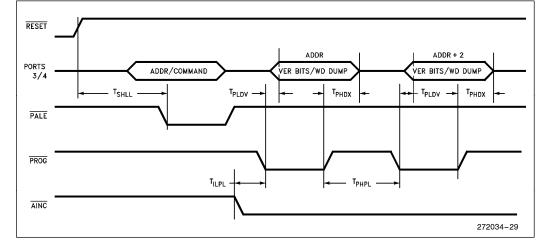

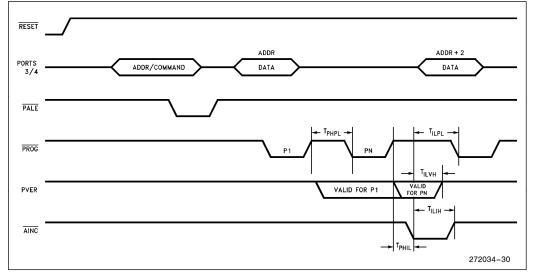

### **AC EPROM PROGRAMMING CHARACTERISTICS**

| Symbol            | Description                  | Min  | Max | Units            |

|-------------------|------------------------------|------|-----|------------------|

| T <sub>SHLL</sub> | Reset High to First PALE Low | 1100 |     | T <sub>OSC</sub> |

| T <sub>LLLH</sub> | PALE Pulse Width             | 40   |     | T <sub>OSC</sub> |

| T <sub>AVLL</sub> | Address Setup Time           | 0    |     | T <sub>OSC</sub> |

| T <sub>LLAX</sub> | Address Hold Time            | 50   |     | T <sub>OSC</sub> |

| T <sub>LLVL</sub> | PALE Low to PVER Low         |      | 60  | T <sub>OSC</sub> |

| T <sub>PLDV</sub> | PROG Low to Word Dump Valid  |      | 50  | T <sub>OSC</sub> |

| T <sub>PHDX</sub> | Word Dump Data Hold          |      | 50  | T <sub>OSC</sub> |

| T <sub>DVPL</sub> | Data Setup Time              | 0    |     | T <sub>OSC</sub> |

| T <sub>PLDX</sub> | Data Hold Time               | 50   |     | T <sub>OSC</sub> |

| T <sub>PLPH</sub> | PROG Pulse Width             | 40   |     | T <sub>OSC</sub> |

| T <sub>PHLL</sub> | PROG High to Next PALE Low   | 120  |     | T <sub>OSC</sub> |

| T <sub>LHPL</sub> | PALE High to PROG Low        | 220  |     | T <sub>OSC</sub> |

| T <sub>PHPL</sub> | PROG High to Next PROG Low   | 120  |     | T <sub>OSC</sub> |

| T <sub>PHIL</sub> | PROG High to AINC Low        | 0    |     | T <sub>OSC</sub> |

| T <sub>ILIH</sub> | AINC Pulse Width             | 40   |     | T <sub>OSC</sub> |

| T <sub>ILVH</sub> | PVER Hold after AINC Low     | 50   |     | T <sub>OSC</sub> |

| T <sub>ILPL</sub> | AINC Low to PROG Low         | 170  |     | T <sub>OSC</sub> |

| T <sub>PHVL</sub> | PROG High to PVER Low        |      | 90  | T <sub>OSC</sub> |

## **DC EPROM PROGRAMMING CHARACTERISTICS**

| Symbol | Description                           | Min | Мах | Units |

|--------|---------------------------------------|-----|-----|-------|

| Ipp    | VPP Supply Current (When Programming) |     | 100 | mA    |

## **EPROM PROGRAMMING WAVEFORMS**

#### SLAVE PROGRAMMING MODE DATA PROGRAM MODE WITH SINGLE PROGRAM PULSE

#### SLAVE PROGRAMMING MODE IN WORD DUMP OR DATA VERIFY MODE WITH AUTO INCREMENT

## SLAVE PROGRAMMING MODE TIMING IN DATA PROGRAM MODE WITH REPEATED PROG PULSE AND AUTO INCREMENT

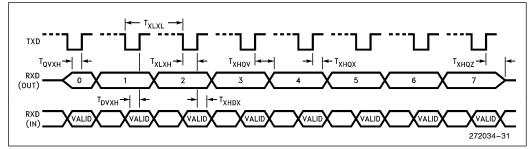

## AC CHARACTERISTICS—SERIAL PORT—SHIFT REGISTER MODE

| Symbol            | Parameter                                                       | Min                     | Мах                     | Units |

|-------------------|-----------------------------------------------------------------|-------------------------|-------------------------|-------|

| T <sub>XLXL</sub> | Serial Port Clock Period (BRR $\ge$ 8002H)                      | 6 T <sub>OSC</sub>      |                         | ns    |

| T <sub>XLXH</sub> | Serial Port Clock Falling Edge to Rising Edge (BRR $\ge$ 8002H) | 4 T <sub>OSC</sub> - 50 | 4 T <sub>OSC</sub> + 50 | ns    |

| T <sub>XLXL</sub> | Serial Port Clock Period (BRR $=$ 8001H)                        | 4 T <sub>OSC</sub>      |                         | ns    |

| T <sub>XLXH</sub> | Serial Port Clock Falling Edge to Rising Edge (BRR $=$ 8001H)   | 2 T <sub>OSC</sub> — 50 | 2 T <sub>OSC</sub> + 50 | ns    |

| T <sub>QVXH</sub> | Output Data Setup to Clock Rising Edge                          | 2 T <sub>OSC</sub> - 50 |                         | ns    |

| T <sub>XHQX</sub> | Output Data Hold after Clock Rising Edge                        | 2 T <sub>OSC</sub> - 50 |                         | ns    |

| T <sub>XHQV</sub> | Next Output Data Valid after Clock Rising Edge                  |                         | 2 T <sub>OSC</sub> + 50 | ns    |

| T <sub>DVXH</sub> | Input Data Setup to Clock Rising Edge                           | $T_{OSC} + 50$          |                         | ns    |

| T <sub>XHDX</sub> | Input Data Hold after Clock Rising Edge                         | 0                       |                         | ns    |

| T <sub>XHQZ</sub> | Last Clock Rising to Output Float                               |                         | 2 T <sub>OSC</sub>      | ns    |

#### SERIAL PORT TIMING—SHIFT REGISTER MODE

## WAVEFORM—SERIAL PORT—SHIFT REGISTER MODE

#### SERIAL PORT WAVEFORM—SHIFT REGISTER MODE

## FUNCTIONAL DEVIATIONS

Devices marked with an "E", "F", or "G" have the following errata.

#### **1. HIGH SPEED INPUTS**

The High Speed Input (HSI) has three deviations from the specifications.

#### NOTE:

"Events" are defined as one or more pin transitions. "Entries" are defined as the recording of one or more events.

- A. The resolution is nine states instead of eight states. Events occurring on the same pin more frequently than once every nine states may be lost.

- B. A mismatch between the nine state HSI resolution and the eight state hardware timer causes one time-tag value to be skipped every nine timer counts. Events may receive a time-tag one count later than expected.

- C. If the FIFO and Holding Register are empty, the first event will transfer into the Holding Register, leaving the FIFO empty again. The next event that occurs will be the first event loaded into the empty FIFO. If the first two events into an empty FIFO (not counting the Holding Register) occur coincident with each other, both are recorded as one entry with one time-tag. If the second event occurs within 9 states after the first, the events will be entered separately with time-tags at least one count apart. If the second event enters the FIFO coincident with the "skipped" time-tag situation (see B above) the time-tags will be at least two counts apart.

#### 2. CMPL with R0

Using CMPL with register 0 can set incorrect flags. Don't use register 0 with the compare long instruction. Use another long word register and set it equal to zero. See Techbit MC0692.

### **REVISION HISTORY**

This data sheet (272034-003) is valid for devices marked with an "E", "F", or "G" at the end of the top side tracking number. Data sheets are changed as new device information becomes available. Verify with your local Intel sales office that you have the latest version before finalizing a design or ordering devices.

The following differences exist between this data sheet and the previous version (-002).

- 1. This data sheet added the ROMless and ROM devices 80C198 and 83C198 respectively.

- 2. The description of the A/D converter prescalar bit was improved.